MediaTek and RDA WiFi Microcontrollers

Published

by Thorsten von Eicken

At https://blog.voneicken.com/2018/lp-wifi-other/

In

Running Wifi Microcontrollers on Battery

Tagged

Low-Power

,

Wifi

Unisoc’s RDA5981 and MediaTek’s MT7697 microcontrollers (as well as variants of these two) also incorporate a WiFi radio on the chip and target low-power embeded IoT applications.

Unisoc RDA5981

The RDA5981 incorporates an ARM Cortex-M4 core with 352KB RAM and 1MB flash in one chip.

The HLK-M50 is one low-cost module that incorporates the chip and I’m expecting one in the mail

soon. In the meantime I’ve taken a closer look at the

datasheet

to see what I might expect.

The RDA5981 incorporates an ARM Cortex-M4 core with 352KB RAM and 1MB flash in one chip.

The HLK-M50 is one low-cost module that incorporates the chip and I’m expecting one in the mail

soon. In the meantime I’ve taken a closer look at the

datasheet

to see what I might expect.

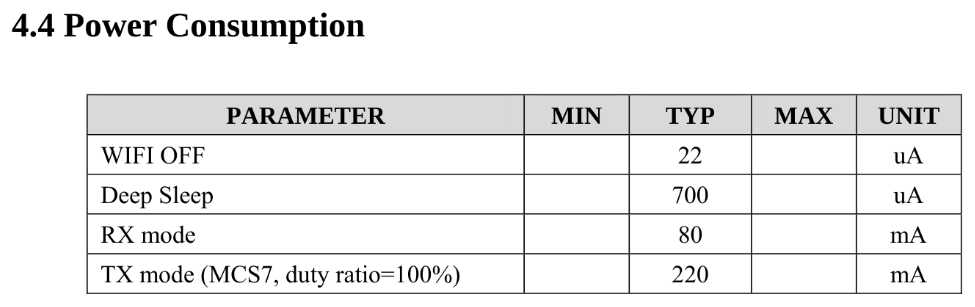

One interesting feature of the chip is that its recommended supply voltage range is from 3.3V to 4.2V, which means that one can run it straight off a LiPo without regulator! A first glipse at what to expect in terms of power consumption is provided by the following table from the datasheet:

The deep-sleep, RX and TX mode power levels look very comparable to the other microcontrollers examined so far. I don’t know what the “WIFI OFF” refers to but I wonder whether it’s really supposed to read 22 milliamperes with the CPU running and the RF section being off.

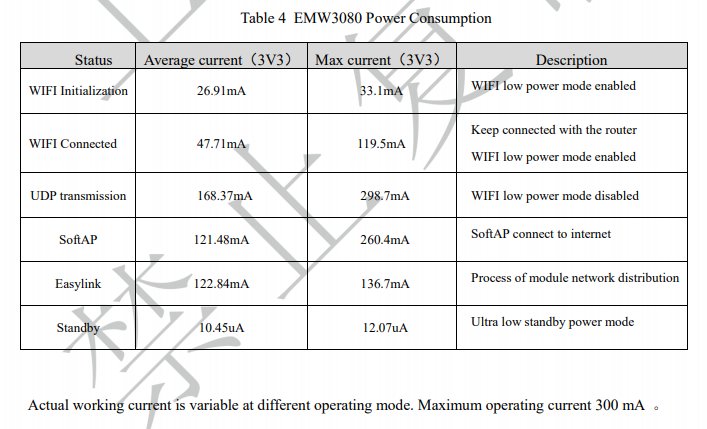

Another module which uses the RDA5891 is MxChip’s EMW3080 and A_D Electronics uncovered a more interesting power consumption table in its docs:

Is this table the power consumption while Wifi is connected is listed at 47mA, which certainly does not compete with the Espressif microcontrollers or the RTL8710. But as seen with the other microcontrollers, until the thing is running some test apps on the bench it’s impossible to tell what the actual power consumption will be.

MediaTek MT7697

The MT7697 is a little different from all the other microcontrollers examined so far in that it

includes a separate processor for the Wifi portion. The application processor is an ARM Cortex-M4

with on-board RAM and a Flash interface. The Wifi processor is unspecified but some of the diagrams

show that it’s also an ARM processor. While this dual-core set-up might look similar to the ESP32 it

differs in that the two microprocessors are completely separated and the Wifi processor is not

accessible to application code at all.

The MT7697 is a little different from all the other microcontrollers examined so far in that it

includes a separate processor for the Wifi portion. The application processor is an ARM Cortex-M4

with on-board RAM and a Flash interface. The Wifi processor is unspecified but some of the diagrams

show that it’s also an ARM processor. While this dual-core set-up might look similar to the ESP32 it

differs in that the two microprocessors are completely separated and the Wifi processor is not

accessible to application code at all.

One of the benefits of the dual-processor architecture is that the application processor can be completely shut down when sleeping while keeping the Wifi processor active to maintain a connection to the access point. The downside is that there’s more to power when both are on.

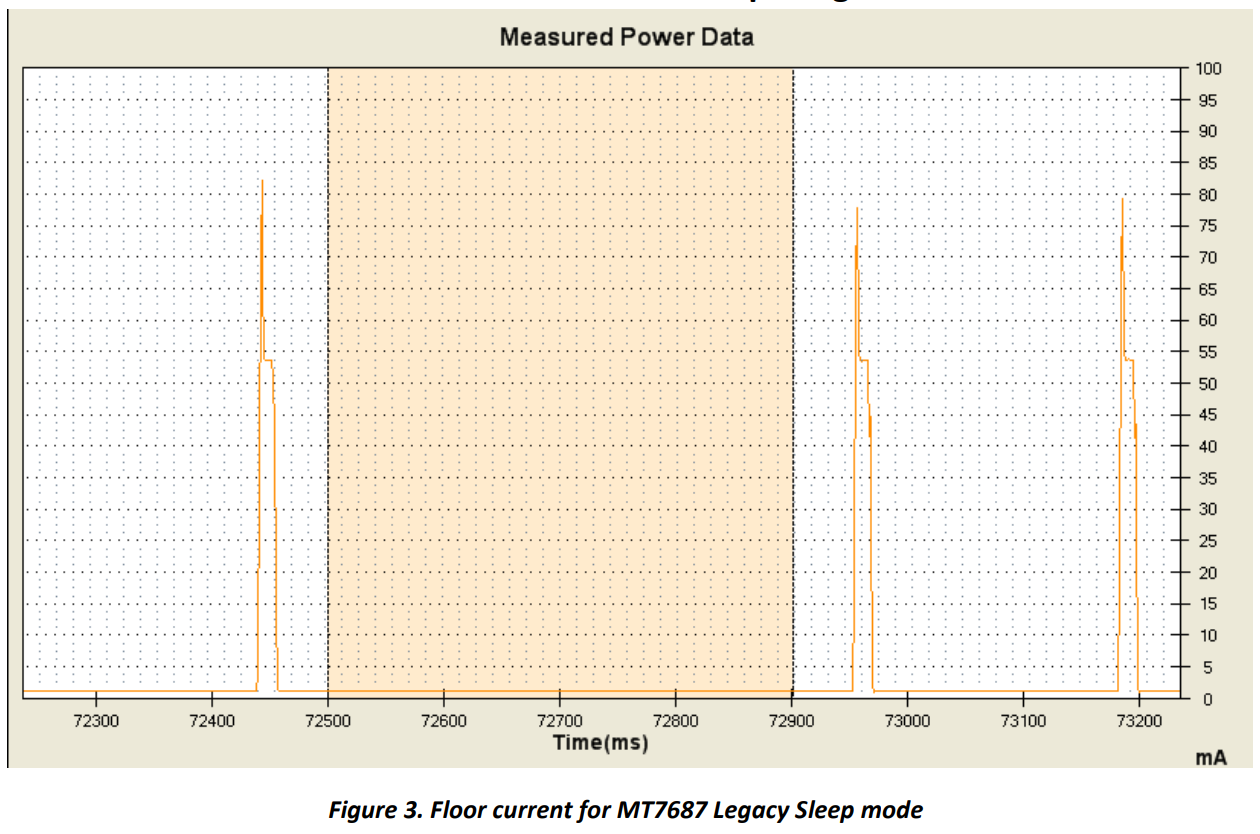

The most interesting document I’ve found so far is the power mode developer’s guide which shows a 9.6mA sleep mode using FreeRTOS tickless idle and a 1.1mA “legacy sleep” mode:

Another interesting document on low power modes has the following table:

| Scenario | Typical Results [mA] |

|---|---|

| Legacy Sleep | 0.667 |

| WiFi Radio off (tickless) | 10.79 |

| WiFi Radio off (legacy sleep) | 0.97 |

| WiFi Connected (DTIM 1, tickless) | 14.18 |

| WiFi Connected (DTIM 1, legacy cleep tickless) | 4.64 |

| WiFi Connected (DTIM10, legacy sleep tickless) | 2.07 |

That looks right in the ballpark of the esp32 to me, but only experimentation will tell for sure…

Stay tuned for the next post…